L'architettura di Trinity

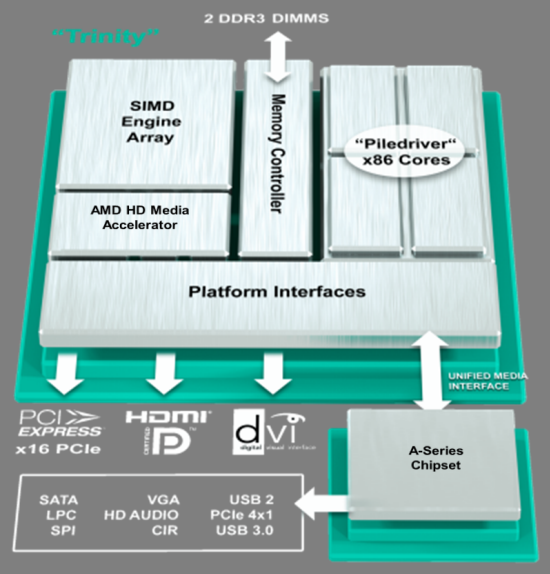

Le nuove APU A-Series per notebook sono disponibili in configurazioni che variano per TDP, da 17W, 25W e 35W (le versioni desktop continuano ad avere un TDP di 65W o 100W come per Llano) con due o quattro core x86 “Piledriver” a 32nm i quali derivano la loro architettura dai core “Bulldozer” utilizzati da AMD per le CPU di fascia più alta della serie FX. Nello stesso die il produttore ha integrato una GPU della serie Radeon HD 7000 con supporto per le API DirectX 11 e, immancabilmente, un controller delle memorie, un controller PCI Express ed il Northbridge.

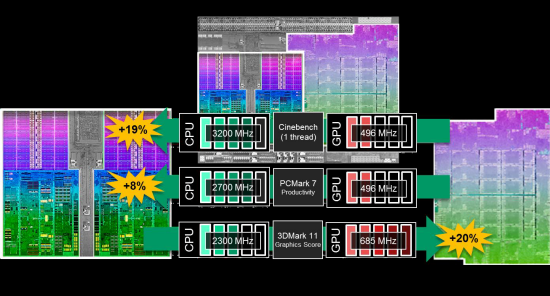

Le frequenze di funzionamento dei componenti interni alla APU sono regolate mediante la tecnologia AMD Turbo Core 3.0 che, nel rispetto del TDP e in base alle richieste dell'applicazione attiva, incrementa o diminuisce ora quelle dei core x86, ora quelle della iGPU.

Il memory controller di Trinity supporta moduli DDR3-1600 comprese le DIMM low power da 1,25V. Qui occorre fare una distinzione con le versioni desktop che, come per la prima generazione di APU Llano, supporteranno memorie DDR3-1866.

La piattaforma Trinity, per poter funzionare, ha bisogno solo di un Fusion Controller Hub (FCH), compiti in questo caso gestiti dall'A70M.

| Caratteristiche tecniche APU notebook AMD A-Series "Trinity" | |

| Tech/Package | -FS1r2 722-pin uPGA, 35x35 mm -FP2 827-pin uBGA, 27x31 mm |

| Tecnologia | 32nm |

| TDP | 17, 25 e 35W (65, 100W Desktop) |

| Core CPU | "Piledriver" 32nm HKMG (fino a 4 core / 2 moduli) Fino a 128 KB L1 Cache (64 KB istruzioni, 64 KB dati) Fino a 4 MB L2 Cache 2 x 128-bit FPU |

| Frequenze CPU | Da 2GHz a 3,8GHz |

| Memorie | DDR3 1600 @ 1.5V LVDDR3 1600 @ 1.35V ULVDDR3 1333 @ 1.25V |

| Core grafici | Fino a 384 Radeon Core 2.0 Supporto DirectX 11 UVD3 AMD Accelerated Video Converter |

| Frequenze GPU | Da 424 a 800 MHz |

| Connessioni display | Digital Display I/F DP0: Display Port, HDMI, DVI Digital Display I/F DP1: Display Port, HDMI, DVI Digital Display I/F DP2: Display Port, HDMI, DVI E' possibile connettere altri display DP 1.2 in daisy-chain LVDS e VGA disponibili con translator VGA su FCH |

| Power Management | Multiple low-power states AMD AllDay power System Management Mode (SMM) ACPI-compliant (supporto P-states, C-states, S0, S3, S4, ed S5) Per compute module power gating (CC6) PCIe core power gating PCIe speed power policy GPU power gating dei Radeon Core e dell'UVD3 AMD Turbo Core 3.0 |

| AMD A70M FCH | |

| Package | FC BGA, 605-Ball, 23x23mm |

| Tecnologia | 65nm |

| Display | DAC integrato per supporto VGA |

| TDP Configs | Da 2,7W a 4,7W |

| UMI | x4 Gen 1 + DP |

| SATA | 6 porte SATA 3.0 |

| RAID | 0,1 |

| USB | 4 USB 3.0 + 10 USB 2.0 + 2 USB 1.1 |

| PCIe | 4x1 Gen2 |

| HWM | Controller ventole e tensioni |

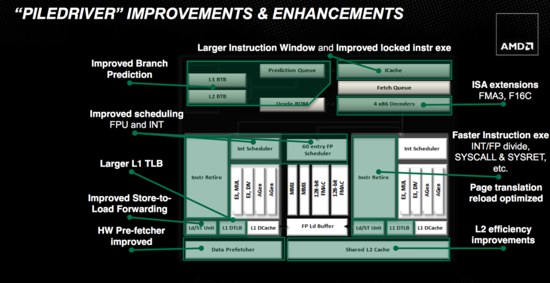

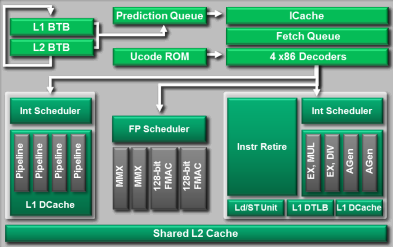

L'architettura del core Piledriver, vista ad alto livello, non differisce molto da quella di Bulldozer dalla quale deriva ma rispetto ad essa prevede diverse ottimizzazioni che la rendono più veloce e più efficiente.

Come per Bulldozer, invece di due core completamente indipendenti ognuno dotato di risorse dedicate, un modulo Piledriver comprende due core x86 che condividono parte delle risorse, in particolare la FPU, la cache L2 e le unità per il recupero e la decodifica delle istruzioni (instruction retirement, registri di load/store).

Alle due ALU indipendenti, dotate ognuna della propria cache L1 dati, del proprio scheduler e delle proprie unità di calcolo, è affiancata una singola unità per i calcoli Floating Point che può gestire le istruzioni di uno dei due thread alla volta, condividendo la cache dati delle due ALU. L'ottimizzazione raggiunta in termini di occupazione di spazio e di banda dati dovrebbe ampiamente ripagare lo scotto prestazionale che comunque bisogna pagare quando si condividono delle risorse hardware.

Rispetto a Bulldozer, AMD ha apportato delle ottimizzazioni al front end utilizzando un design più aggressivo. Lo stesso concetto è stato applicato alla logica flip-flop per garantire una sensibile riduzione dei consumi.

AMD afferma che altri miglioramenti sono stati apportati alle unità di calcolo floating point ed integer, a quelle di branch prediction e prefetch. Il blocco di branch prediction include una nuova unità che tiene conto della storia e lavora in parallelo con l'unità già presente in Bulldozer (e sulla quale ha priorità), mentre il blocco di prefetch di Piledriver segna i dati di prefetch non usati come quelli meno recenti al contrario di Bulldozer, evitando che vengano ricaricati inutilmente.

In Piledriver sono state poi aggiunte le nuove istruzioni FMA3 (in Bulldozer era stato integrato il supporto per le FMA4) ed F16C, in aggiunta a quelle AVX, AVX 1.1 ed AES, per allinearsi all'ISA di Haswell.

Anche di fronte ad un cambio di architettura per le APU, AMD non ha ancora deciso di integrare alcuna cache L3 condivisa fra core x86 e iGPU. La decisione risiede probabilmente nel fatto che con l'attuale tecnologia di processo i benefici prestazionali che se ne avrebbero non andrebbero a bilanciare l'aumento dei consumi e delle dimemsioni del die. In aggiunta, stante l'architettura attuale, una cache L3 siffatta porterebbe più benefici al core grafico integrato - ove AMD è già molto forte - che alla CPU stessa.

Certo è che senza un cambio della tecnologia produttiva AMD non è che poteva fare tanto altro. E in effetti, se compariamo Trinity con Llano guardando al numero di transistor (e area del die) e alle prestazioni raggiunte da CPU e GPU possiamo tranquillamente affermare che le ottimizzazioni ci sono e sono anche molto importanti. Il die è cresciuto meno del 10% mentre le prestazioni della CPU sono superiori di oltre il 20% e quelle della GPU di oltre il 50%. E questo raggiungendo anche consumi inferiori, almeno per quel che concerne le versioni mobile di Trinity.

A contribuire al miglioramento dell'efficienza è anche la tecnologia Turbo Core 3.0 che cerca di bilanciare le prestazioni vs. il TDP di CPU e GPU in maniera completamente dinamica (usando un algoritmo basato sulla trasformata veloce per il calcolo del modello termico che, secondo AMD, restituisce una stima con errore massimo dell'1%). Il Turbo Core di Llano (per i modelli che lo prevedono) è applicato solo ai core x86 mentre la iGPU non va mai oltre la frequenza massima prevista. Nelle APU Trinity, invece, se i core della CPU sono sottoutilizzati, il TDP non sfruttato può andare a beneficio della GPU che così può funzionare ad una frequenza superiore a quella nominale massima.